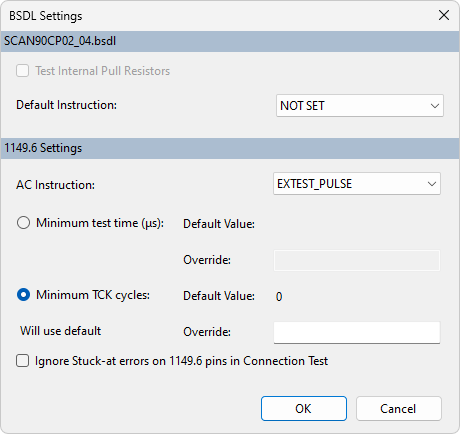

BSDL Settings Dialog

This dialog is reached through the Configure JTAG Device dialog which is in turn accessed from the JTAG Chain screen by clicking  Configure... for a JTAG device. It allows various JTAG options specific to a device or core to be configured.

Configure... for a JTAG device. It allows various JTAG options specific to a device or core to be configured.

- Test Internal Pull Resistors

- Controls whether

internal pull resistors are tested by the connection test. If the BSDL file does not define any internal pull resistors then the checkbox will be disabled. An internal pull resistor is defined where an output cell has a disable result of either PULL0 or PULL1. - Default Instruction

- This is the default state that the device should be put into when it is not being used for input or output. In most cases this does not need to be set, and XJTAG will intelligently manage the state of the device depending on what tests are being carried out and what instructions the device supports.

- 1149.6 Settings

-

If the device is an 1149.6 compliant device then AC settings can be configured for the connection test. These are:

- AC Instruction - The instruction to use during the AC part of 1149.6 testing. The default value is EXTEST_PULSE, but EXTEST_TRAIN can be used if the manufacturer recommends it. Setting it to EXTEST prevents the chip being configured from taking part in the 1149.6 test, and it will behave as a 1149.1-compliant device throughout the connection test.

- Minimum test time - Specifies the minimum number of microseconds which this device must wait between JTAG scans when the AC instruction is being used. Usually this is specified in the BSDL file and so this field does not need to be set.

- Minimum TCK cycles/pulses - When using the EXTEST_PULSE instruction this specifies the minimum number of TCK cycles to carry out between JTAG scans when the AC Instruction is being used. IN EXTEST_TRAIN it specified the minimum number of transitions in the train of signals used when the AC instruction is being used. Usually this is specified in the BSDL file and so this field does not need to be set.

- Ignore Stuck-at errors on 1149.6 pins in Connection Test - This is a workaround for a number of IC designs which have a faulty 1149.6 JTAG implementation, which causes spurious stuck-at errors on unconnected 1149.6-capable inputs. Only set this if the device has this problem, because it reduces test coverage.

The 1149.6 settings will be disabled if the device (as defined in the BSDL file selected) does not support 1149.6 testing.

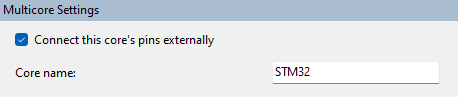

- Multicore Settings

-

If the device is configured as a multicore device then an extra panel is visible allowing the name of the core to be set and whether the pins defined in the core's BSDL file are connected to the external pins of the device. Some multicore devices have cores in the JTAG chain whose pins are only connected internally. Only cores that are connected externally can have their TDO pin selected as the TDO pin of the device.

XJTAG v4.2.6