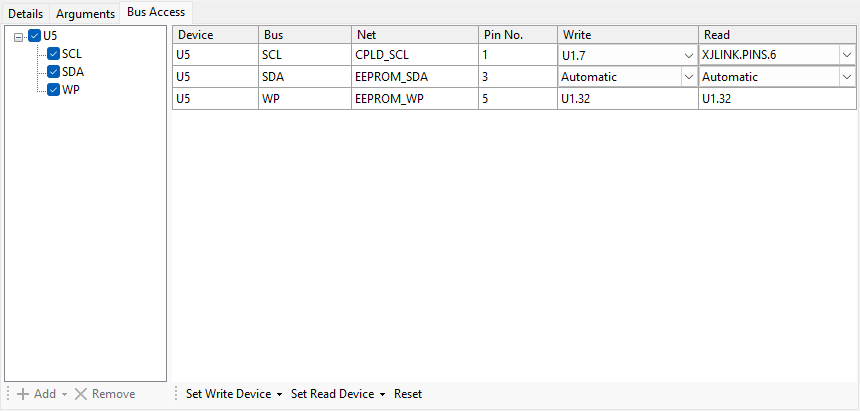

Bus Access Tab

The bus access tab allows fine control over how busses on test devices are read and written.

Device and Bus Selection

The left hand pane lists the busses that are available. Check and uncheck devices and busses here to control what is displayed in the grid to the right.

For a function in a test device file, only busses on that device can be configured and so that device and its busses are automatically displayed.

For a function in circuit code file, there is no obvious default device to display so the pane is initially empty. Instead, any test device from the project can be selected to be configured.

- Click the

Add button to select a test device from the ones available in the project and add it to the pane.

Add button to select a test device from the ones available in the project and add it to the pane. - Select a test device and click the

Remove button to remove a test device from the list.

Remove button to remove a test device from the list.

Writer and Reader Selection

All pins for each bus selected on the left are displayed in the grid on the right. A number of different items can appear in the Write and Read column for each pin:

- If the pin can not be read or written, then Not Readable or Not Writeable is displayed. This cannot be changed.

- If there is only a single option for the reader or writer of that pin, then that item is displayed and cannot be changed.

- If there is more than one way of accessing the pin, then a dropdown is displayed with the various options. By default Automatic is selected, which selects the default behaviour: the XJEase runtime will automatically choose the method of access. Select a different item to force the XJEase runtime to use that method.

All selected busses can be edited at once using the buttons below the grid:

- Click Set Write Device or Set Read Device and select a device from the available list to use that device if possible for all pins. If the selected device is not available for any of the pins, they are left unmodified.

- Click Reset to reset all pins back to using the Automatic method.

Mixed access on logic-driven busses

Often a bus will be driveable through a set of parallel logic gates/buffers which share control signals (enable and/or direction controls). These control signals may even be shared with the test device. If you set such a bus to be partially driven from logic and partially via JTAG pins, the results can be unpredictable, and so it is suggested that you set up such a bus to drive entirely via logic or entirely without using logic rather than a mixture.

XJTAG v4.2.6