Advanced Settings

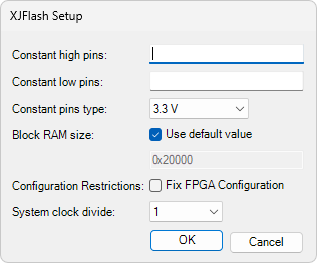

The advanced settings dialog for XJFlash is launched from the second page of the XJFlashSetup configuration wizard.

- Constant high pins and Constant low pins - if there are any pins on your FPGA which need to be at a constant level, in order, for example, to keep it in a configuration mode, they can be entered here.

- Constant pins type - this allows you to select the bank voltage to use for the constant pins.

- Block RAM size - untick the box to change the default value. XJFlash calculates automatically how much RAM it can use for maximum performance. If creating the FPGA image fails, try reducing this to the next lowest power of 2.

- Configuration Restrictions - normally you should leave the Fix FPGA Configuration checkbox unticked. Only tick the box if you have a problem with the number of LUTs/flip-flops required being more than the number available. This will result in a smaller but less configurable XJFlash image being generated.

- System clock divide - if the system fails to build an FPGA image in the next step of the wizard because the system clock is too fast and the FPGA tools cannot meet the necessary timing requirements then this setting will need changing. For best performance, increase the value by only one step at a time then re-check whether the timing requirements have now been met. Note that on a Xilinx Zynq device the clock frequency is dealt with automatically by XJFlash and the clock divide value should always be left at 1.

XJTAG v4.2.6